# High Efficiency, 1MHz, 2A Buck-Boost DC/DC Regulator

## **General Description**

SY9702 is a wide input voltage range, high efficiency, fixed frequency buck-boost converter that operates from input voltage above, below or equal to the output voltage. It provides a power supply for system powered by either a two-cell or three-cell alkaline, Ni-Cd or Ni-MH battery, or a one-cell Li-Ion or Li-polymer battery.

SY9702 can support for 2A load current capability. It is based on a fixed frequency, pulse-width-modulation (PWM) controller using synchronous rectification to obtain maximum efficiency. The output voltage and compensation circuit can be programmed using external resistors and capacitors network. During shutdown, the load is disconnected from the battery. The device is packaged in tight QFN2x3-13.

## **Ordering Information**

| Ordering Number | Package type | Note |

|-----------------|--------------|------|

| SY9702QOC       | QFN2x3-13    |      |

## **Features**

- Fixed frequency operation with battery voltage above, below or equal to the output.

- Four internal power switches to form true 4switches buck-boost with single inductor.

- Seamless buck-boost transition.

- 2.6V to 5.5V Input Voltage Range.

- 2A continuous output current capability.

- Output disconnect at shutdown.

- Power good indicator.

- Compact package: QFN2x3-13

- Built in thermal shut down protection, hard short protection.

## **Applications**

- Palmtop Computers

- Handheld Instruments

- MP3/MP4 Players

- Digital Cameras/Camcorders

- Personal Medical Products

- High Power LED's

- All two-cell and three-cell alkaline, Ni-Cd or Ni-MH or signal-cell Li battery powered products

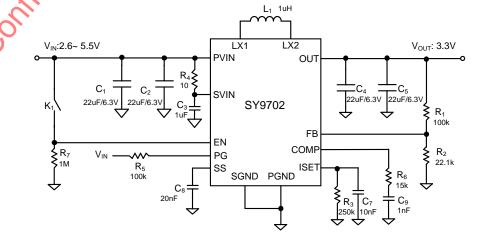

# **Typical Applications**

Figure 1. Schematic diagram

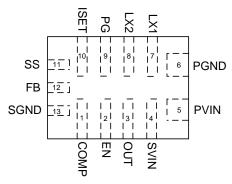

## Pinout (top view)

**Top Mark: ZN**xyz (device code: ZN, x=year code, y=week code, z= lot number code)

| Pin Name | Pin Number  | Description                                                                               |  |  |  |  |  |

|----------|-------------|-------------------------------------------------------------------------------------------|--|--|--|--|--|

| COMP     | 1           | External compensation for voltage loop.                                                   |  |  |  |  |  |

| EN       | 2           | Enable control. Pull high to turn on. Internal integrated with 1M $\Omega$ pull           |  |  |  |  |  |

|          |             | down Resistor.                                                                            |  |  |  |  |  |

| OUT      | 3           | Output of the synchronous rectifier. Decouple this pin to GND with at least               |  |  |  |  |  |

|          |             | 22uF ceramic cap. Minimize the loop area formed by output cap, OUT pin                    |  |  |  |  |  |

|          |             | and GND paddles.                                                                          |  |  |  |  |  |

| SVIN     | 4           | Signal power input pin. Decouple this pin to GND with at least 1uF ceramic                |  |  |  |  |  |

|          |             | cap.                                                                                      |  |  |  |  |  |

| PVIN     | 5           | Power input pin. Decouple this pin to GND with at least 22uF ceramic cap.                 |  |  |  |  |  |

|          |             | Minimize the loop area formed by input cap, PVIN pin and GND paddles.                     |  |  |  |  |  |

| PGND     | 6           | Power ground pin.                                                                         |  |  |  |  |  |

| LX1      | 7           | Inductor connection 1 Connect this node to the switching node of the                      |  |  |  |  |  |

|          |             | inductor.                                                                                 |  |  |  |  |  |

| LX2      | 8           | Inductor connection 2. Connect this node to the switching node of the                     |  |  |  |  |  |

|          | ::(0.       | inductor.                                                                                 |  |  |  |  |  |

| PG       |             | Power good indicator.                                                                     |  |  |  |  |  |

| ISET     | <b>©</b> 10 | Apply a resistor and capacitor parallel network to sense the output average               |  |  |  |  |  |

|          | O           | current. If V <sub>ISET</sub> is lower than 0.2V, IC will go into PFM mode. Do not let it |  |  |  |  |  |

| Š        |             | floating. Tie to ground for forced PWM operation.                                         |  |  |  |  |  |

| SS       | 11          | Connect this pin to a soft-start capacitor to program soft-start time.                    |  |  |  |  |  |

| FB       | 12          | Output feedback pin. Connect this pin to the center point of the output                   |  |  |  |  |  |

|          |             | resistor divider to program the output voltage.                                           |  |  |  |  |  |

| SGND     | 13          | Signal ground pin.                                                                        |  |  |  |  |  |

# **Absolute Maximum Ratings** (Note 1)

| OUT                                 | 4 V    |

|-------------------------------------|--------|

| All Other Pins                      | 6V     |

| Power Dissipation, PD @ TA = 25°C   | 3W     |

| Package Thermal Resistance (Note 2) |        |

| heta ja                             | 40°C/W |

| $\theta$ JC                         | 18°C/W |

| Junction Temperature Range          | 150°C  |

| Lead Temperature (Soldering, 10 sec.)            | 260°C        |

|--------------------------------------------------|--------------|

| Storage Temperature Range                        |              |

| Storage Temperature Range                        |              |

| <b>Recommended Operating Conditions</b> (Note 3) |              |

| Supply Input Voltage                             | 2.6V to 5.5V |

| Output Voltage                                   | 2.6V to 3.8V |

| Junction Temperature Range                       |              |

| Ambient Temperature Range                        | 40°C to 85°C |

# cilerol Conidential For Helia Intito

### **Electrical Characteristics**

$(V_{IN} = 4.2V, V_{OUT} = 3.3V, L = 1 \mu H, C_{OUT} = 22 u Fx2, T_A = 25 ^{\circ}C, I_{OUT} = 1 A unless otherwise specified)$

| Parameter                       | Symbol             | Test Conditions                                                                 | Min   | Тур  | Max   | Unit       |

|---------------------------------|--------------------|---------------------------------------------------------------------------------|-------|------|-------|------------|

| Input Voltage Range             | $V_{\rm IN}$       |                                                                                 | 2.6   |      | 5.5   | V          |

| Output Voltage Range            | $V_{\mathrm{OUT}}$ |                                                                                 | 2.6   |      | 3.8   | V          |

| Quiescent Current               | $I_Q$              | $I_{OUT}$ =0, EN=1,<br>ISET=250k $\Omega$ ,<br>FB=105%*V <sub>REF</sub>         |       | 60   | 100   | μΑ         |

| Shutdown Current                | $I_{SHDN}$         | EN=0                                                                            |       | 0.1  | 1     | μA         |

| Feedback Reference Voltage      | $V_{ m REF}$       |                                                                                 | 0.591 | 0.6  | 0.609 | V          |

| NFET R <sub>DS(ON)</sub>        | $R_{DS(ON)1}$      |                                                                                 |       | 50   |       | m $\Omega$ |

| PFET R <sub>DS(ON)</sub>        | $R_{DS(ON)2}$      |                                                                                 |       | 50   |       | m $\Omega$ |

| Input Peak Current Limit        | $I_{LIM}$          |                                                                                 | 4.5   | 5    |       | A          |

| Output Negative Current Limit   | $I_{NEG}$          |                                                                                 |       | -1   |       | A          |

| Soft-start current              | $I_{SS}$           | Soft-start time:<br>$t_{ss} = \frac{0.7 \text{V}}{\text{I}_{ss}} \times C_{ss}$ |       | 5    |       | μΑ         |

| EN rising threshold             | $V_{\mathrm{ENH}}$ |                                                                                 | 1.5   |      |       | V          |

| EN falling threshold            | V <sub>ENL</sub> × |                                                                                 |       |      | 0.4   | V          |

| Input UVLO rising threshold     | $V_{UVLO}$         |                                                                                 |       | 2.45 | 2.55  | V          |

| UVLO hysteresis                 | $V_{\rm HYS}$      |                                                                                 |       | 0.2  |       | V          |

| PG rising threshold             | $V_{\rm FB,HV}$    |                                                                                 |       | 0.48 |       | V          |

| PG under-voltage threshold      | $V_{ m FB,LV}$     |                                                                                 |       | 0.48 |       | V          |

| PG over voltage threshold       | $V_{\rm FB,OV}$    |                                                                                 |       | 0.72 |       | V          |

| Output current sense            | I <sub>SET</sub>   | I <sub>OUT</sub> =1A                                                            |       | 5    |       | μA         |

| Output Voltage Over Protection  | $V_{OVP}$          |                                                                                 |       | 125  |       | %          |

| OVP protection delay time       | TovP_delay         |                                                                                 |       | 16   |       | μs         |

| ISET pin threshold for PFM mode | $V_{ m PFM}$       |                                                                                 |       | 0.2  |       | V          |

| Oscillator Frequency            | Fosc               | I <sub>OUT</sub> =1.0A                                                          | 0.8   | 1.0  | 1.2   | MHz        |

| Min Duty Cycle                  |                    | Boost & Buck                                                                    |       | 10   |       | %          |

| Max Duty Cycle                  |                    | Boost & Buck                                                                    |       | 90   |       | %          |

| Thermal Shutdown Temperature    | $T_{SD}$           |                                                                                 |       | 150  |       | °C         |

| Thermal Shutdown Hysteresis     | $T_{HYS}$          |                                                                                 |       | 15   |       | °C         |

**Note 1** Stresses beyond the "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note 2:  $\theta_{JA}$  is measured in the natural convection at  $T_A = 25^{\circ}C$  on a low effective single layer thermal conductivity test board of JEDEC 51-3 thermal measurement standard. Paddle of QFN2x3-13 package is the case position for  $\theta_{JC}$  measurement.

Note 3: The device is not guaranteed to function outside its operating conditions.

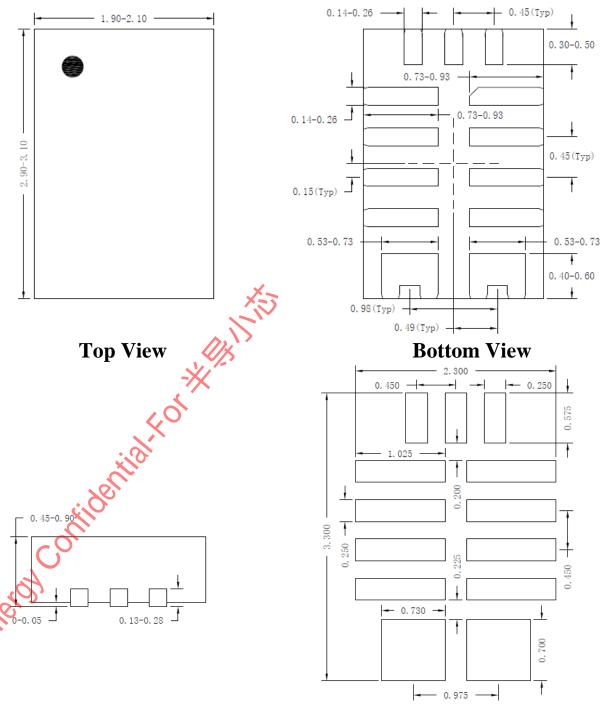

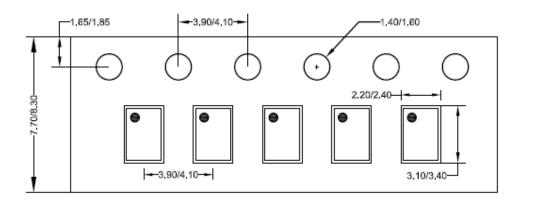

# QFN2x3-13 Package Outline Drawing

**Side View**

Recommended PCB layout (Reference Only)

Notes: All dimension in millimeter and exclude mold flash & metal burr.

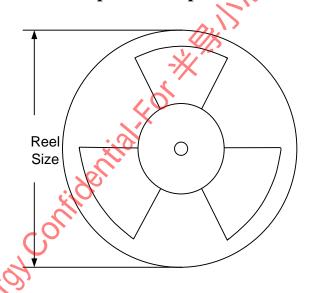

## **Taping & Reel Specification**

## 1. QFN2x3-13 taping orientation

Feeding direction -----

# 2. Carrier Tape & Reel specification for packages

| Package<br>type | Tape width (mm) | Pocket pitch(mm) | Reel size<br>(Inch) | Trailer<br>length(mm) | Leader length (mm) | Qty per<br>reel |

|-----------------|-----------------|------------------|---------------------|-----------------------|--------------------|-----------------|

| QFN2x3          | 8               | 4                | 7''                 | 400                   | 160                | 3000            |

## 3. Others: NA